- 课程目录

- 相关资源

- 课程笔记

电源设计小贴士49:多层陶瓷电容器常见小缺陷的规避方法

因其小尺寸、低等效串联电阻(ESR)、低成本、高可靠性和高纹波电流能力,多层陶瓷 (MLC) 电容器在电源电子产品中变得极为普遍。一般而言,它们用在电解质电容器 leiu 中,以增强系统性能。相比使用电解电容器铝氧化绝缘材料时相对介电常数为 10 的电解质,MLC 电容器拥有高相对介电常数材料 (2000-3000) 的优势。这一差异很重要,因为电容直接与介电常数相关。在电解质的正端,设置板间隔的氧化铝厚度小于陶瓷材料,从而带来更高的电容密度。

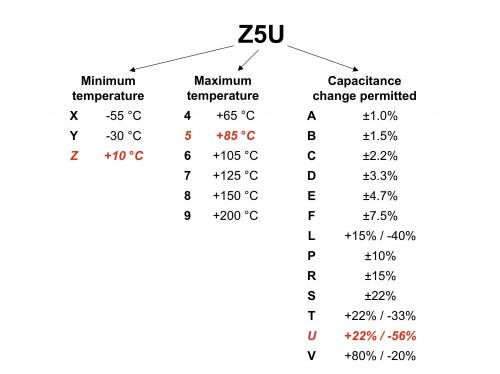

温度和 DC 偏压变化时,陶瓷电容器介电常数不稳定,因此我们需要在设计过程中理解它的这种特性。高介电常数陶瓷电容器被划分为 2 类。图 1 显示了如何以 3 位数描述方法来对其分类,诸如:Z5U、X5R 和 X7R 等。例如,Z5U 电容器额定温度值范围为 +10 到 +85o C,其变化范围为 +22/–56%。再稳定的电介质也存在一定的温度电容变化范围。

图 1 :2类电介质使用 3 位数进行分类。注意观察其容差!

当我们研究偏压电容依赖度时,情况变得更加糟糕。图 2 显示了一个 22 uF、6.3伏、X5S 电容器的偏压依赖度。我们常常会把它用作一个 3.3 伏负载点 (POL) 稳压器的输出电容器。3.3 伏时电容降低 25%,导致输出纹波增加,从而对控制环路带宽产生巨大影响。如果您曾经在 5 伏输出时使用这种电容器,则在温度和偏压之间,电容降低达 60% 之多,并且由于 2:1 环路带宽增加,可能产生一个不稳定的电源。许多陶瓷电容器厂商都没有详细说明这一问题。

图 2:注意电容所施加偏压变化而降低

陶瓷电容器的第二个潜在缺陷是,它们具有相对较小的电容和低ESR。在频域和时域中,这会带来一些问题。如果它们被用作某个电源的输入滤波电容器,则它们很容易随输入互连电感谐振,形成一个我们在《电源设计小贴士3》和《电源设计小贴士 4》中讨论的振荡器。要想知道是否存在潜在问题,可将寄生互连电感估算为每英寸 15 nH,然后根据这两篇文章介绍的方法把滤波输出阻抗与电源输入电阻进行对比。第二个潜在问题存在于时域中,我们可在以太网电源 (POE) 等系统中看到它们的踪影。

在这些系统中,电源通过大互连电感连接至负载。负载通过一个开关实现开启,并可能会使用陶瓷电容器构建旁路。这种旁路电容器和互连电感可以形成一个高 Q谐振电路。由于负载电压振铃可以高达电源电压的两倍,因此在负载下关闭开关会形成一个过电压状态。这会引起意外电路故障。例如,在 POE 中,负载组件的额定电压变化可以高达电源额定电压的两倍。

第三个潜在缺陷的原因是陶瓷电容器为压电式。也就是说,当电容器电压变化时,其物理尺寸改变,从而产生可听见的噪声。例如,我们将这种电容器用作输出滤波电容器时(存在大负载瞬态电流),或者在“绿色”电源中,其在轻负载状态下进入突发模式。这种问题的变通解决方案如下:

- 转而使用更低介电常数的陶瓷材料,例如:COG 等。

- 使用不同的电介质,例如:薄膜等。

- 使用加铅和表面贴装技术 (SMT) 组件,可紧密贴合印制线路板 (PWB)。

- 使用更小体积器件,降低电路板应力。

- 使用更厚组件,降低施加电压应力和物理变形。

SMT陶瓷电容器存在的另一个问题是,在PWB弯曲时,由于电容器和 PWB 之间存在的热膨胀系数 (TCE) 错配,它们的软焊接头往往会裂开。您可以采取一些预防措施来减少这种问题的发生:

- 封装尺寸限制为 1210。

- 使电容器远离高曲率地区,例如:拐角区等。

- 使电容器朝向电路板短方向。

- 使电路板安装点远离边角。

- 在所有装配过程均注意可能出现的电路板弯曲。

总之,如果您注意其存在的一些小缺点,则相比电解电容器,多层陶瓷电容器拥有低成本、高可靠性、长寿命和小尺寸等优势。它们具有非常宽的电容容差范围,因此您需要对其温度和偏压变化范围内的性能进行评估。它们均为压电式,其意味着它们会在有脉冲电流的系统中产生可听见的噪声。最后,它们很容易出现破裂,因此我们必须采取预防措施来减少这一问题的发生。所有这些问题都有相应的解决办法。因此,MLC 电容器仍会变得越来越受欢迎。

下次,我们将继续讨论开关式电源的电容器选择,敬请期待。

推荐帖子

- 关于STM32的管脚映射的问题

- 在STM32中有个函数 GPIO_PinRemapConfig 函数库里面说的是改变管脚的映射 这个怎样理解啊 ...

-

爱好汽车电子

TI技术论坛

TI技术论坛

- 有些话想说

- 昨天看到了gaoyang9992006发的帖子,原文如下:“好想有个MSP430板子我是学C primer plus起家的单片机爱好者,由于囊中羞涩只能玩玩几块钱的STC51单片机,后来听说MSP430是另一种类型的单片机,就借本书学习了,发现端口的使用跟51比起来完全是另外一码事情,哎呀,没想到用端口还要先定义,O(∩_∩)O~,以前不懂了。每个端口都可以进行中断,这个倒是挺有意思的。哎,不知道...

-

wstt

微控制器 MCU

微控制器 MCU

- 触摸子板发送安排名单

- 截止到目前位置,触摸子板已经全部在安排发送。 因为期间还需要2、3天的安排时间,所以快递单号要迟些告诉大家。 有朋友特别着急,先将发送名单列在这里吧 ...

-

soso

微控制器 MCU

微控制器 MCU

- 请教LaunchPad学习中的出现问题

- 最近学习LaunchPad时发现,官方所给的几款芯片好像都不支持UART,只支持SPI和I2C,请问大侠们是这样的吗?还有,这几款芯片中的datasheet中都没有关于其USI模块功能的详细说明,小弟在图书馆查阅各种资料也没找到类似说明,请问各位大侠指点...

-

jiyiboloann

微控制器 MCU

微控制器 MCU

京公网安备 11010802033920号

京公网安备 11010802033920号